Логические триггеры что это?

Логические триггеры что это?

Триггер — простейшее последовательностное устройство, которое может находиться в одном из двух возможных состояний и переходить из одного состояния в другое под воздействием входных сигналов. Триггер является базовым элементом последовательностных логических устройств. Входы триггера разделяют на информационные и управляющие (вспомогательные). Это разделение в значительной степени условно. Информационные входы используются для управления состоянием триггера. Управляющие входы обычно используются для предварительной установки триггера в некоторое состояние и для синхронизации.

Триггеры классифицируют по различным признакам, поэтому существует достаточно большое число классификаций. К сожалению, эти классификации не образуют стройной системы, но инженеру необходимо их знать.

Классификация триггеров

- по способу приема информации;

- по принципу построения;

- по функциональным возможностям.

Асинхронный триггер

Асинхронный триггер – изменяет свое состояние непосредственно в момент появления соответствующего информационного сигнала.

Синхронные триггеры

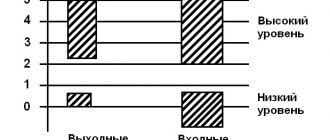

Синхронные триггеры в свою очередь подразделяют на триггеры со статическим (статические) и динамическим (динамические) управлением по входу синхронизации C. Статические триггеры воспринимают информационные сигналы при подаче на вход C логической единицы (прямой вход) или логического нуля (инверсный вход).

Динамические триггеры воспринимают информационные сигналы при изменении (перепаде) сигнала на входе C от 0 к 1 (прямой динамический С-вход) или от 1 к 0 (инверсный динамический С-вход).

Статические триггеры

Статические триггеры в свою очередь подразделяют на одноступенчатые (однотактные) и двухступенчатые (двухтактные). В одноступенчатом триггере имеется одна ступень запоминания информации, а в двухступенчатом — две такие ступени. Вначале информация записывается в первую ступень, а затем переписывается во вторую и появляется на выходе. Двухступенчатый триггер обозначают через ТТ.

Различие триггеров по функциональным возможностям

- с раздельной установкой состояния 0 и 1 (RS-триггеры);

- универсальные (JK-триггеры);

- с приемом информации по одному входу D (D-триггеры, или триггеры задержки);

- со счетным входом Т (Т-триггеры).

Обозначение входов триггеров

Входы триггеров обычно обозначают следующим образом:

S — вход для установки в состояние «1»;

R — вход для установки в состояние «0»;

J — вход для установки в состояние «1» в универсальном триггере;

К — вход для установки в состояние «0» в универсальном триггере;

Т — счетный (общий) вход;

D — вход для установки в состояние «1» или в состояние «0»;

V — дополнительный управляющий вход для разрешения приема информации (иногда используют букву Е вместо V).

Рассмотрим некоторые типы триггеров и их реализацию на логических элементах.

Асинхронный RS-триггер

Обратимся к асинхронному RS-триггеру, имеющему условное графическое обозначение, приведенное на рис. 3.54.

Триггер имеет два информационных входа: S (от англ. set) и R (от англ. reset).

Закон функционирования триггеров удобно описывать таблицей переходов, которую иногда также называют таблицей истинности (рис. 3.55). Через S’, R’, Q’ обозначены соответствующие логические сигналы, имеющие место в некоторый момент времени t, а через Qt + 1 — выходной сигнал в следующий момент времени t+1.

Комбинацию входных сигналов S’ = l, R’ =1 часто называют запрещенной, так как после нее триггер оказывается в состоянии (1 или 0), предсказать которое заранее невозможно. Подобных ситуаций нужно избегать.

Рассматриваемый триггер может быть реализован на двух элементах ИЛИ-НЕ (рис. 3.56).

Необходимо убедиться, что эта схема функционирует в полном соответствии с приведенной выше таблицей переходов.

Микросхема К564ТР2 содержит 4 асинхронных RS-триггера и один управляющий вход (рис. 3.57).

В асинхронном RS-триггере на элементах И-НЕ переключение производится логическим «0», подаваемым на вход R или S, т. е. реализуется обратная рассмотренной ранее таблица переходов (рис. 3.58). Запрещенная комбинация соответствует логическим «0» на обоих входах.

Синхронный RS-триггер

Рассмотрим синхронный RS-триггер (рис. 3.59).

Если на входе С — логический «0», то и на выходе верхнего входного элемента «И-НЕ», и на выходе нижнего будет логическая «1». А это, как отмечалось выше, обеспечивает хранение информации.

Если же на вход синхронизации С подана логическая единица, то схема реагирует на входные сигналы точно так же, как и рассмотренная ранее (рис. 3.56).

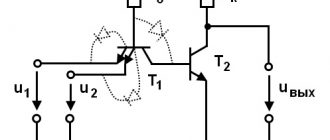

Триггер типа MS

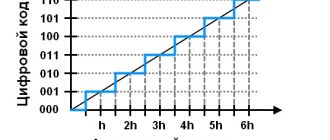

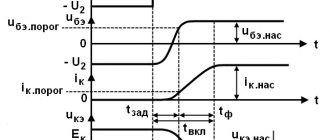

Рассмотрим принцип построения двухступенчатого триггера, который называют также триггером типа MS (от англ. master, slave, что переводят обычно как «ведущий» и «ведомый»). Его упрощенная структурная схема приведена на рис. 3.60. В схеме имеются два одноступенчатых триггера (ведущий М и ведомый S) и два электронных ключа (Кл1 и Кл2).

Временная диаграмма сигнала синхронизации, поясняющая работу триггера, приведена на рис. 3.61.

Рассмотрим ряд временных интервалов указанной диаграммы:

t < ta — ведущий триггер отключен от информационных входов, ведомый триггер подключен к ведущему;

ta < t < tb — ведущий триггер отключен от информационных входов, ведомый триггер отключен от ведущего;

tb < t < tc — ведущий триггер подключен к информационным входам, ведомый триггер отключен от ведущего. В ведущий триггер записывается информация, поданная на входы;

tc < t < td — ведущий триггер отключен от информационных входов, ведомый триггер отключен от ведущего;

td < t — ведущий триггер отключен от информационных входов, ведомый триггер подключен к ведущему, информация из ведущего триггера переписывается в ведомый. Это происходит сразу после момента времени td и означает, что фактически двухступенчатый триггер срабатывает при изменении сигнала синхронизации от 1 к 0. При этом выходные сигналы определяются теми входными информационными сигналами, которые имели место непосредственно перед отрицательным фронтом сигнала синхронизации.

JK-триггер

Рассмотрим JK-триггер (от англ. jump иkeep), отличающийся от рассмотренного RS-триггера тем, что появление на обоих информационных входах (J и К) логических единиц (для прямых входов) приводит к изменению состояния триггера. Такая комбинация сигналов для JK-триггера не является запрещенной.

В остальном JK-триггер подобен RS-триггеру, причем роль входа S играет вход J, а роль входа R — вход К.

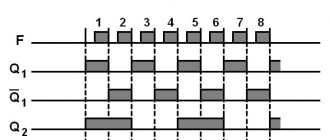

JK-триггеры реализуют в виде триггеров типа MS или в виде динамических триггеров (т. е. JK-триггеры являются синхронными).

На рис. 3.62 приведено условное графическое обозначение двухступенчатого JK-триггера.

Обратимся к динамическим триггерам. Для них характерно блокирование информационных входов в тот момент, когда полученная информация передается на выход. Нужно отметить, что в отношении реакции на входные сигналы динамический триггер, срабатывающий при изменении сигнала на входе С от 1 к 0, подобен рассмотренному двухступенчатому триггеру, хотя они отличаются внутренним устройством.

Для прямого динамического С-входа используют обозначения, приведенные на рис. 3.63, а, а для инверсного динамического С-входа, используют обозначения, приведенные на рис. 3.63, б.

D-триггер

Рассмотрим D-триггер (от англ. delay), повторяющий на своем выходе состояние входа. Рассуждая чисто теоретически, D-триггер можно образовать из любых RS- или JK-триггеров, если на их входы одновременно подавать взаимно инверсные сигналы (рис. 3.64).

Условное графическое обозначение D-триггера приведено на рис. 3.65.

Т-триггер

Рассмотрим Т-триггер, который изменяет свое логическое состояние на противоположное по каждому активному сигналу на информационном входе Т. Условное графическое обозначение двухступенчатого Т-триггера приведено на рис. 3.66.

Спасибо, пригодилось на экзамене. Сдал нормально)

Спасибо за информацию.!